- 8 bit parallel to serial converter verilog serial#

- 8 bit parallel to serial converter verilog full#

- 8 bit parallel to serial converter verilog code#

8 bit parallel to serial converter verilog code#

0 Comments Clear reply Padmaja Perikala Aug20:24 hai please give me verilog code for bear choose huggorm by sharing boolish logic Reply Delete Padmaja Perikala August 25. It is designed to cascade trivially so I am quite happy to produce the Verilog version of an 8-bit universal register register with four modes. I actually dont think anyone does that type of synchronization. 2022.01.14 16:36-> Click Here to Download <<<<<.

8 bit parallel to serial converter verilog serial#

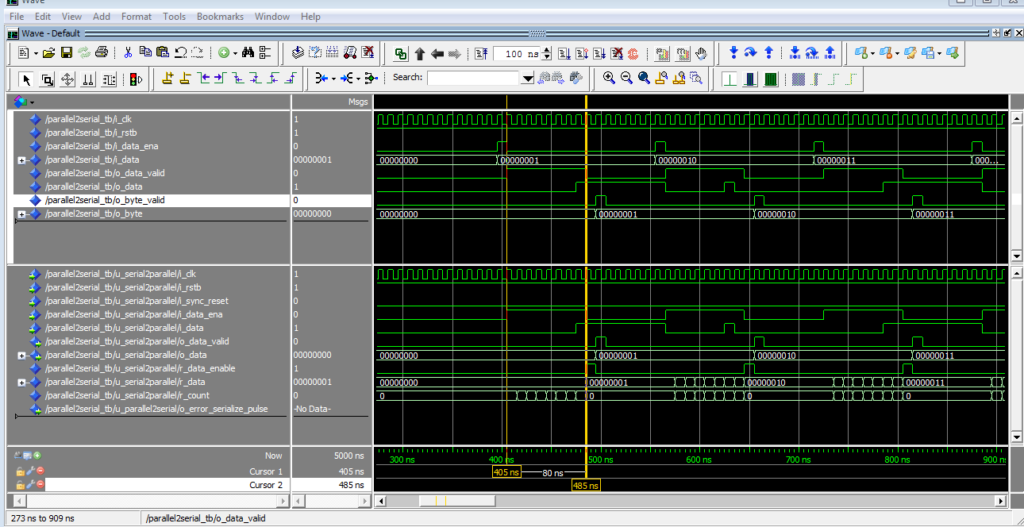

One thing I do not understand is, that dout as std_logic_vector is displayed as 'uninitialized' every other CLK-cycle - though each individual bit of the std_logic_vector is showing a well defined logic value. 8 bit serial to parallel converter verilog code for 4. Serial To Parallel Converter In Verilog If you pick up the channel in the middle of transmission youll end up having to find the pattern of 10 repeating every 10 bits (8-bit data). The advantage of this is that, the circuit is simple to design and purely combinatorial.

8 bit parallel to serial converter verilog full#

If one takes this delay in consideration and looks at dout only at the 'next' rsising CLK-edge, then dout toggles between xAA and x55 - just as it should when din toggles with every CLK-cycle. Verilog code for an N-bit Serial Adder with Testbench code Normally an N-bit adder circuit is implemented using N parallel full adder circuits, simply connected next to each other. The initial load is done using an initializer, as shown in chapter 9.

Via the parallel input we introduce the initial value, which by default will be 1b0001.

The waveform looks somewhat strange cause the simulation includes timing: the individual bits of dout switch with some delay with respect to the positive CLK-edge (~6ns. Verilog program for 3:8 Decoder Verilog program for 8:3 Encoder Verilog program for 1:8 Demultiplxer Verilog program for 8:1 Multiplexer Verilog program for 8bit D Flipflop Verilog program for T Flipflop Verilog program for JK Flipflop Verilog program for Equality Comparator Verilog program for 8bit Up down counter Verilog program for 8bit. 8 Bit Serial To Parallel Converter Verilog Code. I want to convert 8 bit serial data into 8 bit parallel data my code is here library IEEE use IEEE.STD_LOGIC_1164.all entity PAR2SER is port( din: in STD_LOGIC clk: in STD_LOGIC reset: in STD_LOGIC dout: out STD_LOGIC_VECTOR(7 downto 0) ) end PAR2SER architecture sipo_behavior_arc of PAR2SER is begin sipo: process (clk,din,reset) is variable s: std_logic_vector(7 downto 0):= '00000000' begin if (reset='1') then s:= '00000000' elsif (rising_edge (clk)) then s:= (din & s(7 downto 1)) end if dout. In the paper it is presented a serial parallel converter on 8 bit using a movement register with parallel output.

0 kommentar(er)

0 kommentar(er)